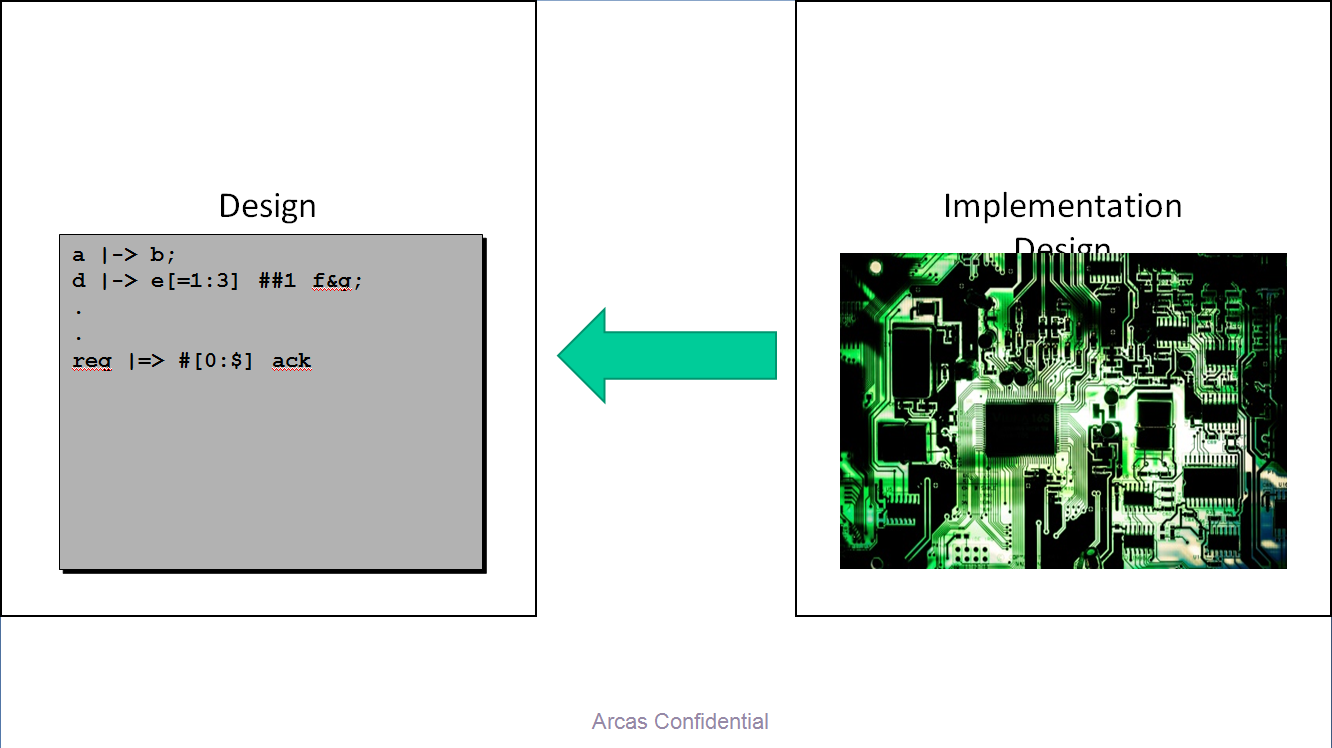

Functional feature verification applied to chip design is replacing simulation verification with more and more application scenarios. It is used by the user to provide the attributes and constraints required for verification according to the design requirements, and to answer these attributes correctly by mathematical induction and reasoning. If it is not correct, it will automatically generate a stimulus chain that can be used for simulation to facilitate troubleshooting. The mathematical rigor of formal verification makes it a must-have for chip designs that require extreme safety and reliability.

Compared to simulation verification, the advantages of formal verification include the fact that no user is required to generate test stimuli. The authenticity of an attribute is based on a rigorous mathematical proof – a property that proves to be true will not be erroneously simulated under any excitation. The completeness of formal verification depends on the completeness of the attribute, while the latter can establish a clear and unambiguous model based on the design requirements, which has great advantages compared with the incompletely imperfect simulation coverage that has been plagued by simulation verification. Since the attributes can be based on any signal and runtime scenario within the design, formal verification also has the advantage of white box verification, while simulation can only determine right or wrong at the output. In addition, functional form verification is applicable to all stages of the design, especially in the early stage of the module-level design stage. In the case of extremely difficult to build a simulation environment, which is helpful for early detection of design errors and reduction of design iterations.